呼!在效能解禁前,先來了解下全線首發 8 顆 Ryzen 9、7、5 的 3000 系列處理器,以及 7nm、Zen2 架構下的革新,如何榨出 +15% IPC 的效能提升。而下一篇就等待 7/7 號解禁,在帶來 Ryzen 的效能、遊戲測試,以及 Navi 的遊戲測試囉!

全線首發 8 顆 Ryzen 9、7、5 的 3000 系列處理器

全線首發 8 顆 Ryzen 9、7、5 的 3000 系列處理器

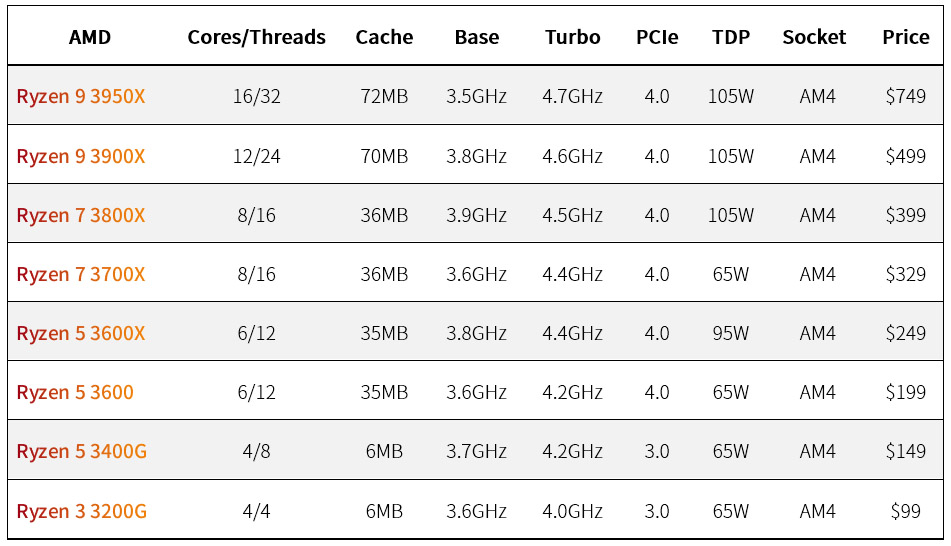

AMD CEO Dr. Lisa Su 於今年 COMPUTEX CEO Keynote 首發第三代 Ryzen 3000 系列處理器,又在 E3 Live 活動中給出 16 核心的驚喜 Ryzen 9 3950X,這波 7/7 號上市的名單就有著 7 顆 Ryzen 9、7、5 的 3000 系列處理器,而 Ryzen 9 3950X 稍晚於今年 9 月推出。

↑ Ryzen 3000 系列規格表。

玩家可比對上表處理器規格,Ryzen 9 有著 3900X 12C24T 與 3950X 16C32T 處理器,這兩顆原為 Threadripper(TR4)系列規格,但這次因 Zen2 的架構升級,下放至 Ryzen AM4 平台。

時脈方面,3900X 最高 4.7GHz Turbo、3950X 4.6GHz Turbo,可見這兩顆天身體質都不錯,而兩者皆是 105W TDP,只不過定價策略 3950X / $749、3900X / $499,這價格差異確實有點大,但與同核心的競品相比,恩!還行阿。

Ryzen 7 的 3800X 與 3700X 都是 8C16T 處理器,僅差異在時脈、價格與 TDP。3800X 是整個系列中預設最高 3.9GHz 的基礎時脈,但 Turbo 僅 4.5GHz,而相較 3700X 則是 3.6 / 4.4GHz。只不過預設下 3800X 為 105W TDP、3700X 65W TDP,主要是讓玩家、系統商可有不同的選擇,再加上 3800X / $399、3700X / $329 定價,可見這代 8C 甜蜜點無疑是 3700X。

↑ Ryzen 7 與 9 都標配 Wraith Prism RGB 信仰風扇。

至於主流 Ryzen 5 的 3600X 與 3600 都是 6C12T 處理器,同樣差異在時脈、TDP 與價格,相對價格對比競品都相當超值。

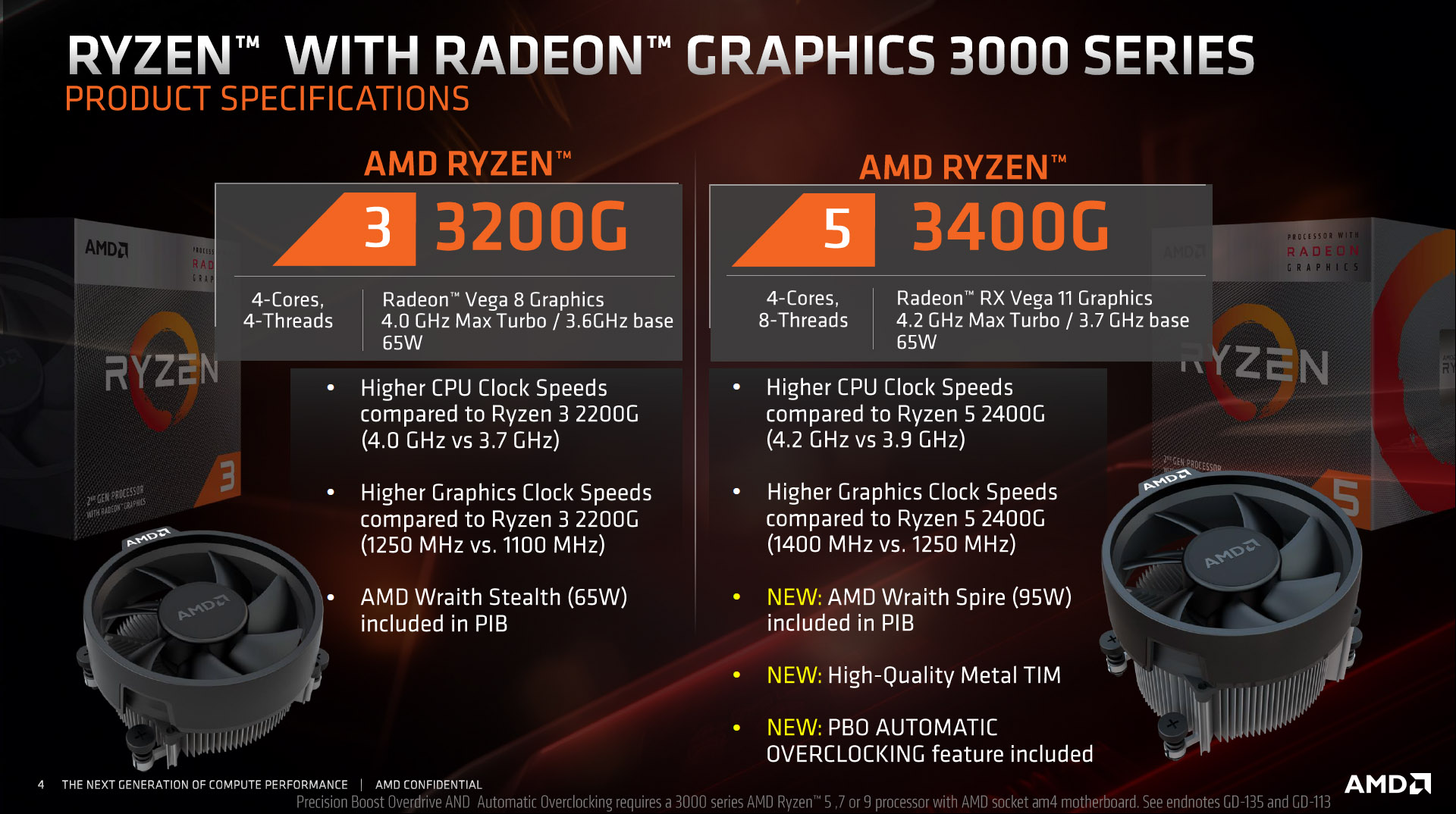

最後,這次首發中還有 Ryzen 5 3400G(Vega 11)4C8T 與 Ryzen 3 3200G(Vega 8)4C4T,這兩顆實際是上代 12nm、Zen+ 產品,但也因此 CPU 與 GPU 時脈雙提升,而且 3400G 不僅定價降低,換 Wraith Spire 95W 散熱器並改用 Metal TIM 導熱介質,這顆 APU 可以期待阿!

↑ Ryzen 5 3400G 價格降、換散熱器、改 Metal TIM,期待。

首殺 7nm “Zen 2” 新架構 15% IPC 提升

首殺 7nm “Zen 2” 新架構 15% IPC 提升

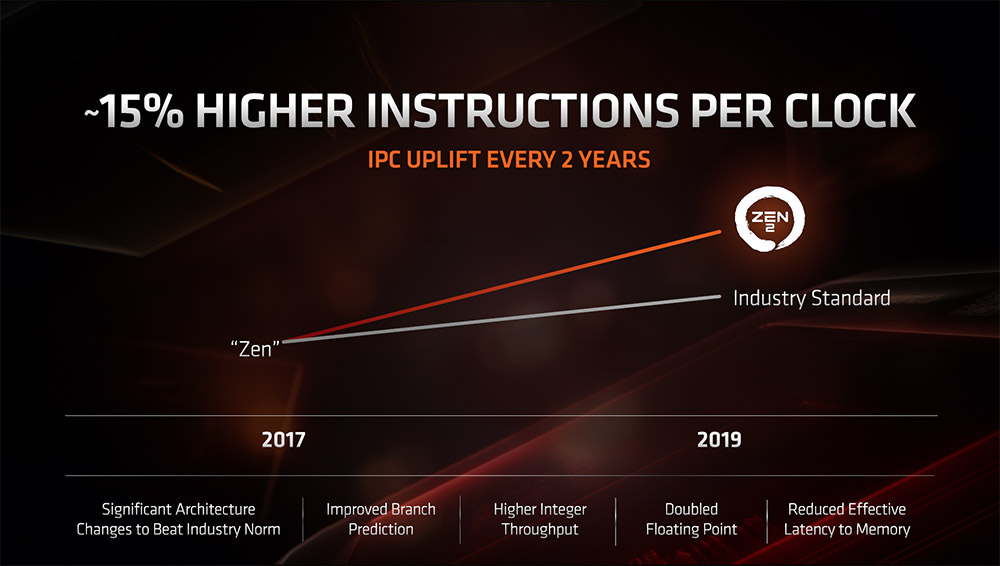

第三代 Ryzen 獲得如此的成功,除了與 TSMC 深度合作 7nm 製程之外,Zen 2 架構的改進也是功不可沒。AMD 僅花 2 年的時間,讓 Zen 2 架構有著 15% Instructions per Clock(IPC)的提升,主要重點在於:強化前端(Front-End)的分支預測(Branch Prediction)設計、提高整數(Integer)吞吐量、加倍浮點數(Floating Point)運算與降低記憶體延遲。

↑ AMD 花 2 年時間讓 Zen 2 提升 15% IPC。

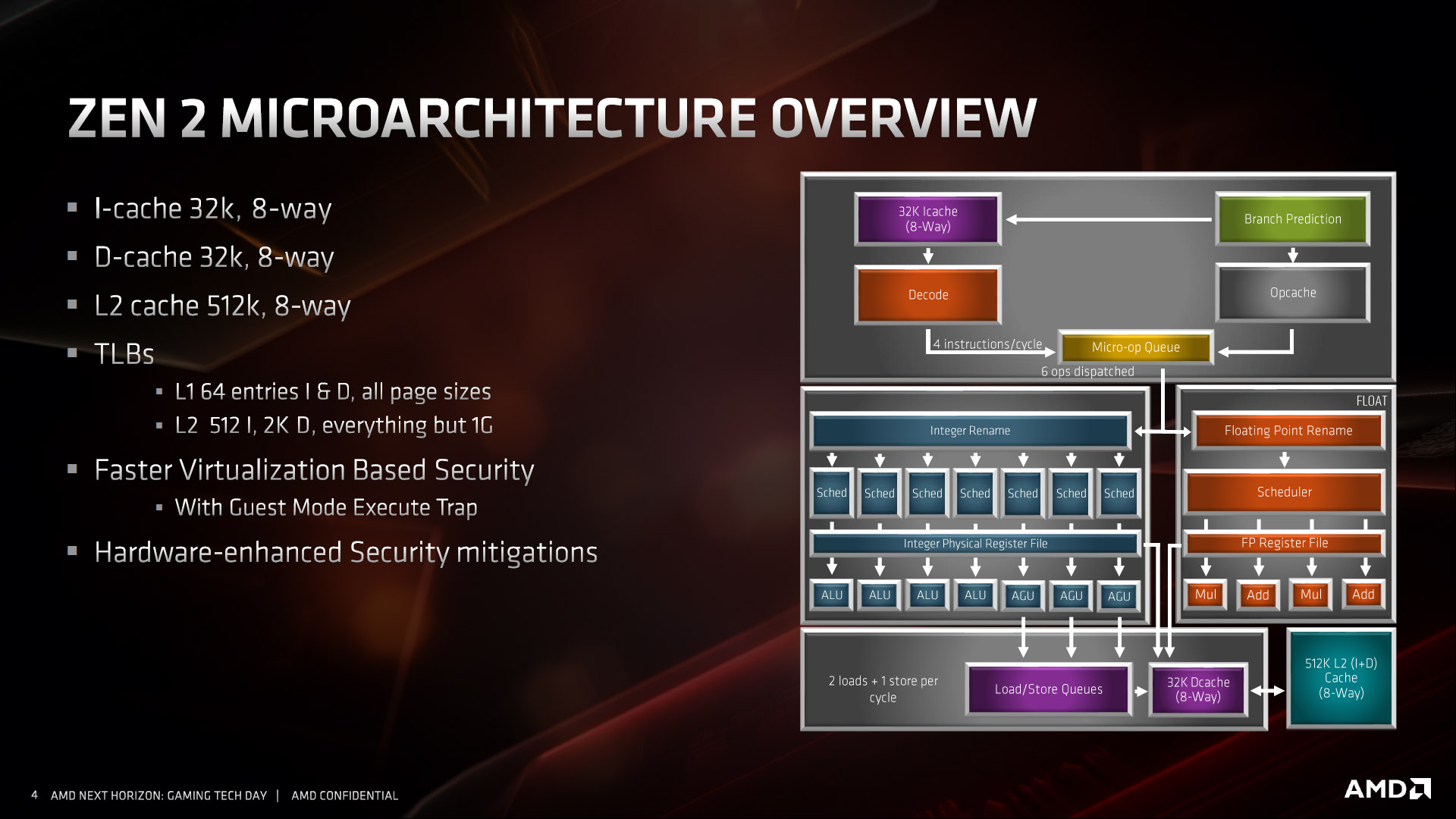

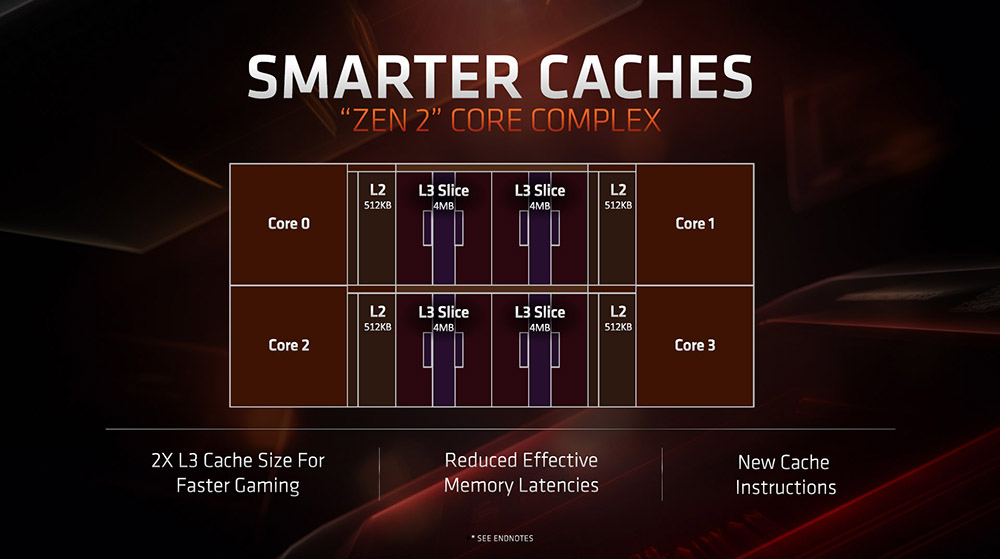

Zen 2 整體架構並無太大的改變,承襲 Zen 系列的設計,但在各部細節精進榨出更多的效能。Zen 2 主要有全新 L2 分支預測 TAGE、加大 Micro Op-Cache、加倍 L3 Chace、4 組 Integer Units 與 3 組 AGUs、3 AGENs per cycle、增加 loads / store 資源與支援 AVX256 浮點數運算。

各級快取也有著通道、容量的改變,以及對於虛擬化安全性、硬體強化安全機制等。

↑ Zen 2 架構改變重點。

↑ Zen 2 架構改變重點。

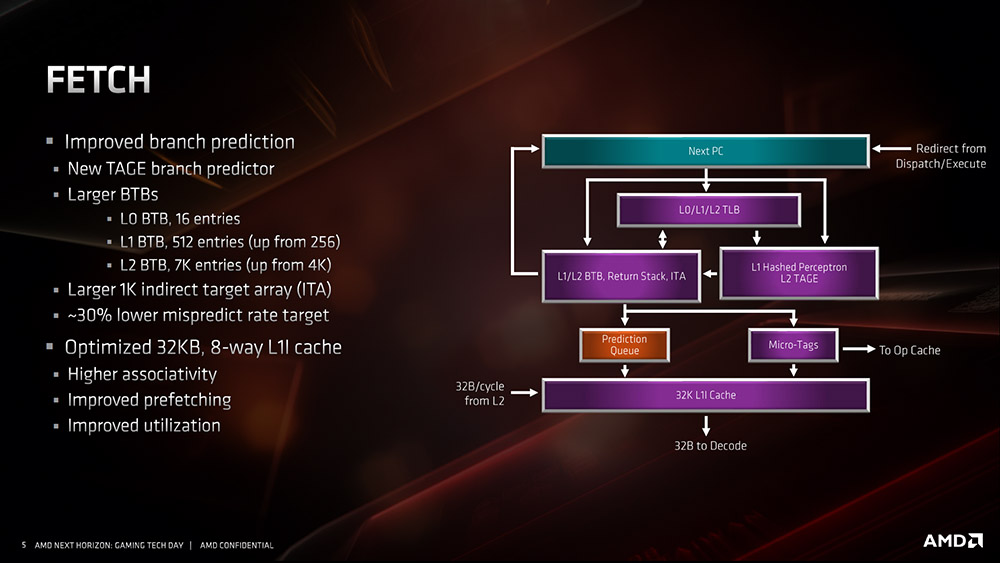

處理器前端的分支預測(Branch Prediction),L1 採用 Hashed Perceptron 預測,盡可能的預取,而 L2 則採用新的 TAGE 預測,以額外的標記實現更長的分支記錄,獲得更好的預測結果。

因此加大 BTB(Branch Target Buffer)分支目標緩衝,記錄更多的指令預測與快取要求,L1 BTB 加大至 512 entry、L2 BTB 加倍至 7K entry,而 L0 BTB 維持 16 entry 不變,此外 Indirect Target Array 加大至 1K entry。

這樣的改變下,可大幅降低 30% 的錯誤預測率。雖然 L1-I Cache 降至 32KB 但提升至 8-way 通道,亦可增加預取與提高使用率。

↑ Fetch。

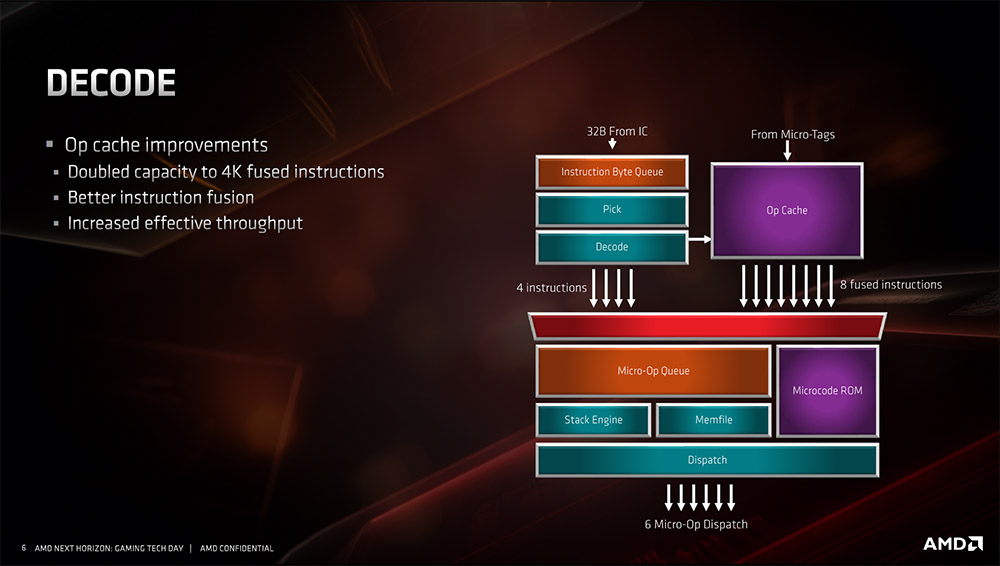

解碼 Decode 方面,Micro-op Cache 加大至 4K entry,比以往儲存更多的解碼指令,並提升調度率給予 8 Fused Instruction 至緩衝的通道;而解碼器依舊 4 Instruction 輸出至緩衝,在一個週期下可輸出 6 Micro-Op Dispatch 調度。

↑ Decode。

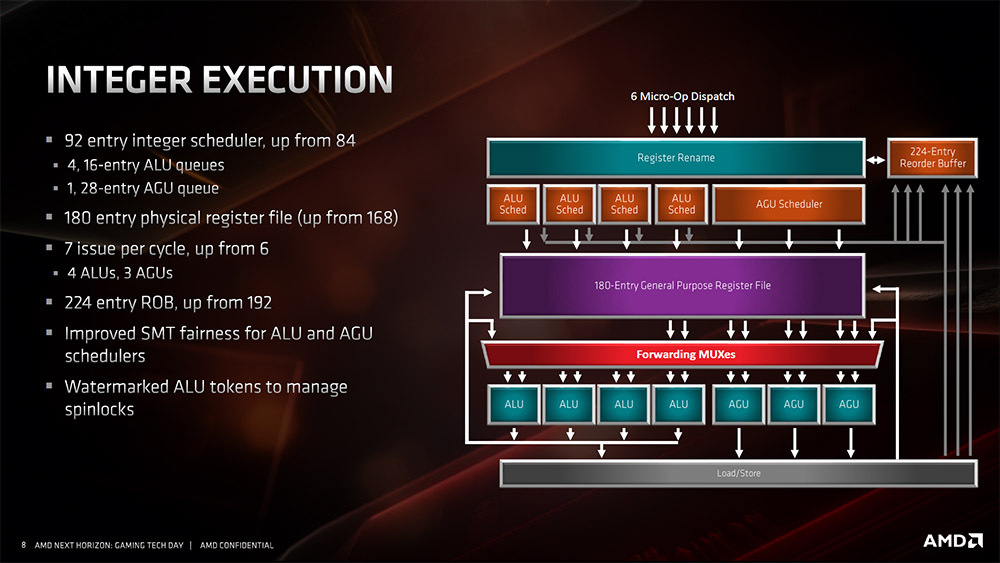

整數 Integer 運算單元,每週期可接收 6 個 Micro-Op Dispatch,至 224 entry Reorder Buffer,而整數單元技術上有著 4 個 16-entry ALU Scheduler、1 個 28-entry AGU Scheduler,共 92 個整數調度器。

同樣每週期可執行 4 ALU、3 AGU 的運算,並加強 SMT 多執行緒的 ALU、AGU 的調度公平,並追蹤特定 ALU 操作,管理自旋鎖(SpinLock)的狀況。

↑ Integer。

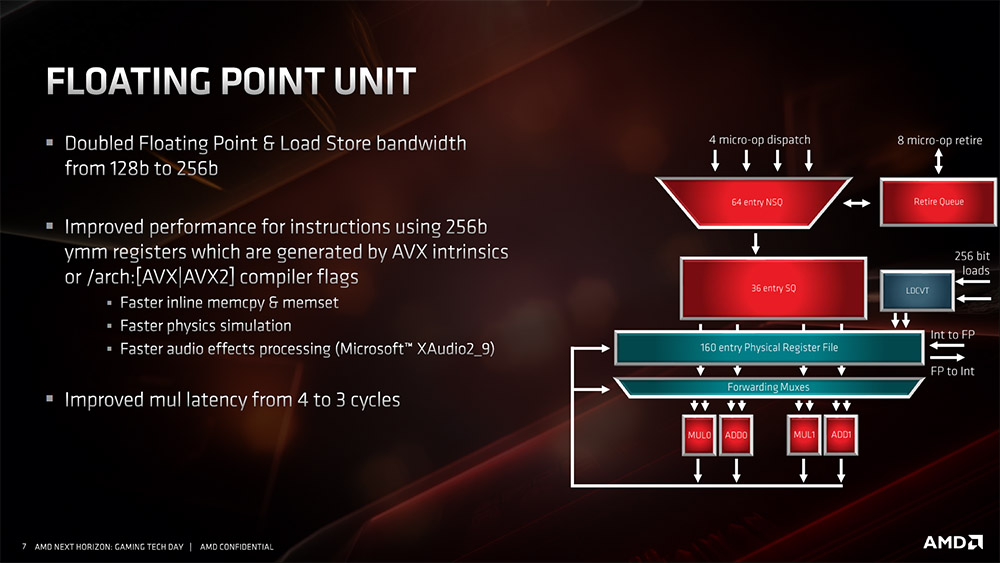

浮點數 Floating Point 運算單元,可說這代一大很有感提升,支援 AVX2 指令,意味著 AMD 加倍 Floating Point 與 Load / Store 頻寬至 256b,因此可在一個週期執行 AVX2 的運算。而 AMD 說道實際運行 AVX 時並無設計降低時脈的設置,但最終可能因功耗、散熱而自動調節。

↑ Floating Point。

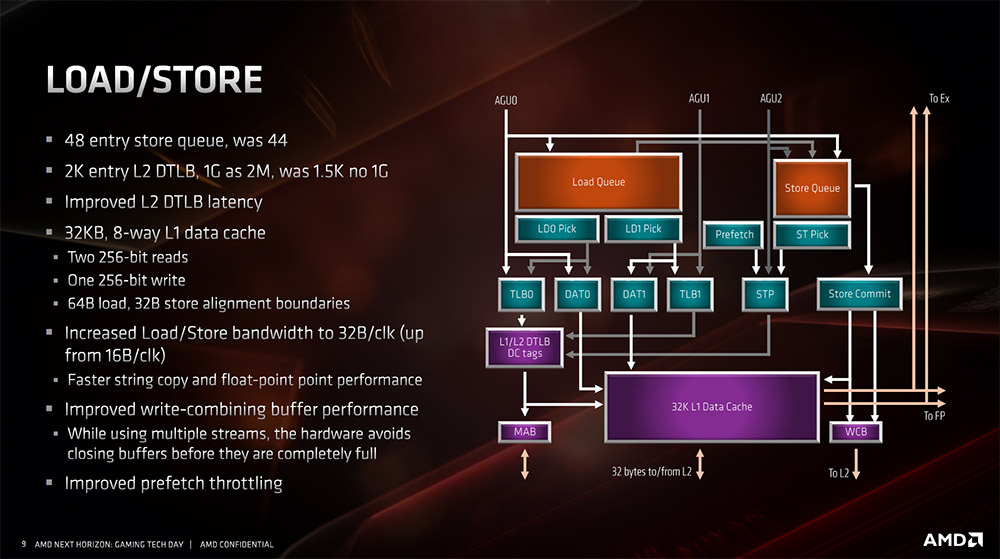

Load / Store 單元,也對應著運算單元的改變,提升至每週期 2 個 256-bit 載入、1 個 256-bit 儲存操作,而 Store Queue 也增加至 48 entry。

↑ Load / Store。

↑ 這代快取主要是加大頻寬、容量。

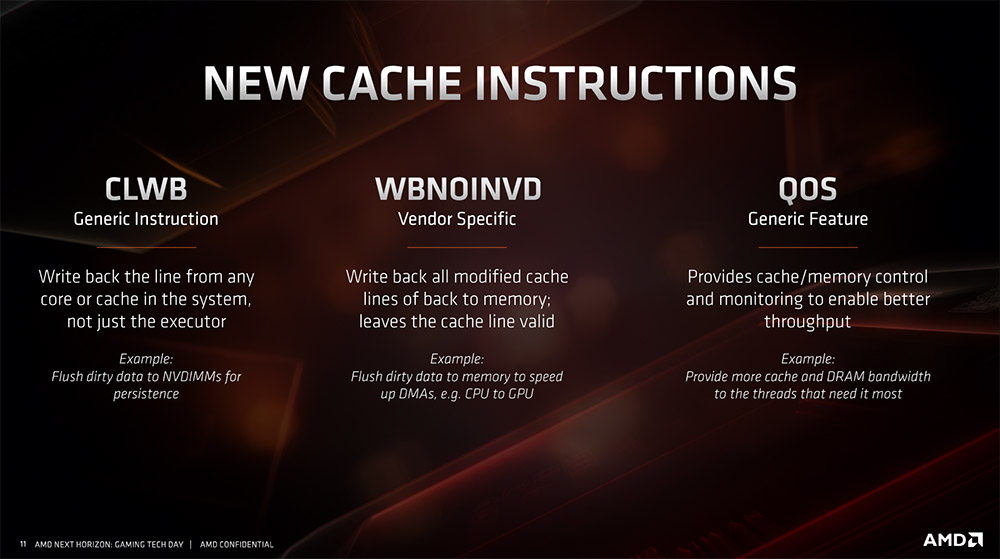

↑ Zen 2 加入新的快取指令:CLWB、WBNOINVD 與 QOS 等。

精進 Chiplet 設計 7nm CCD、12nm cIOD

精進 Chiplet 設計 7nm CCD、12nm cIOD

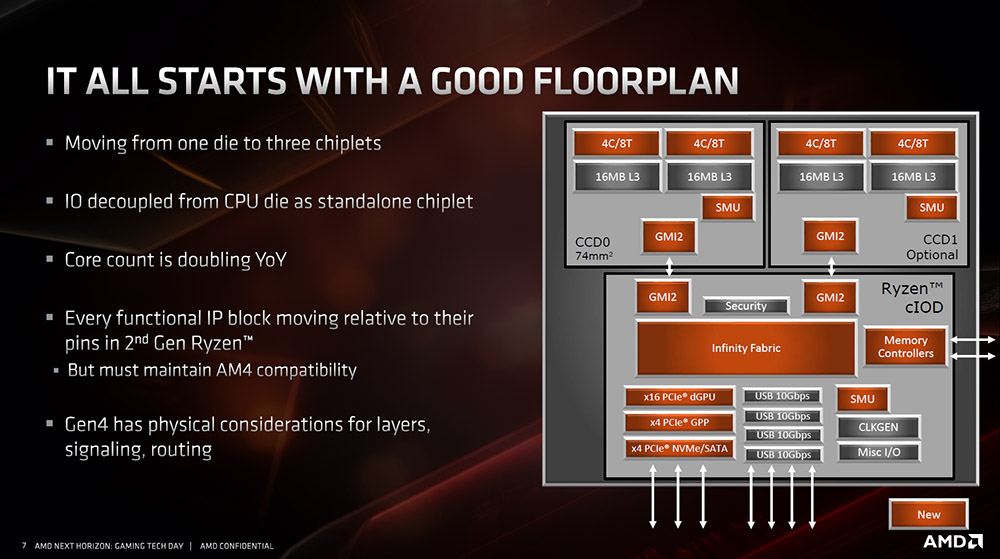

Zen 2 維持著同樣的 Core Complex(CCX)設計,每個 CCX 當中有著 4 個核心以及各自的快取,並將所有對外 I/O 抽離,成為 Chiplet 小核心設計。因此,一顆 Ryzen 處理器,將包含至少一顆 CCD(內含兩顆 CCX)與一顆 cIOD(I/O Die)。

↑ CCX。

↑ CCD + cIOD。

CCD 之間的 2 顆 CCX 相互以 Die-to-Die Infinity Fabric 溝通,並有著 32B/cycle 雙向與 cIOD 的 Data Fabric 傳輸資料;因此 cIOD(I/O Die)主要包含 Data Fabric、記憶體控制與 I/O Hub 等功能。

↑ 路線框架圖。

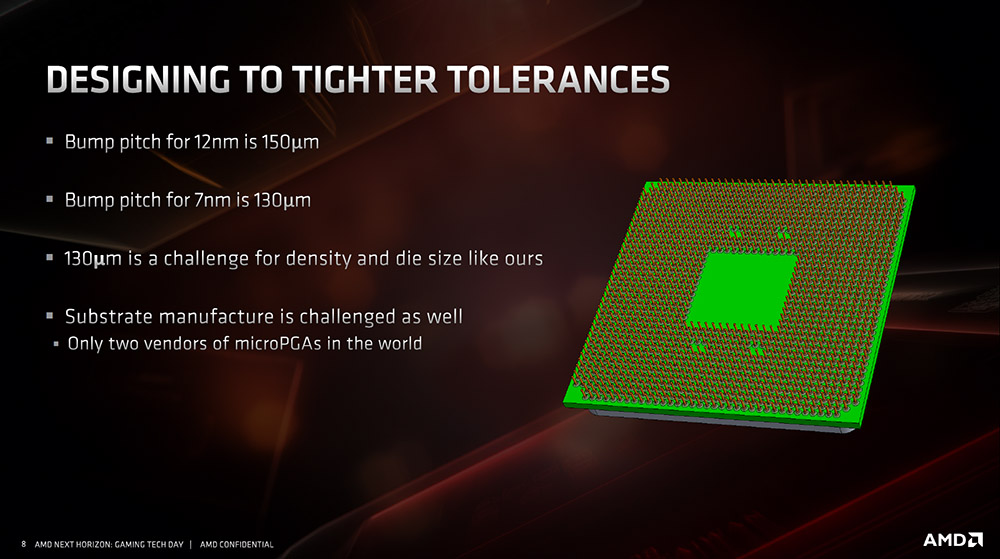

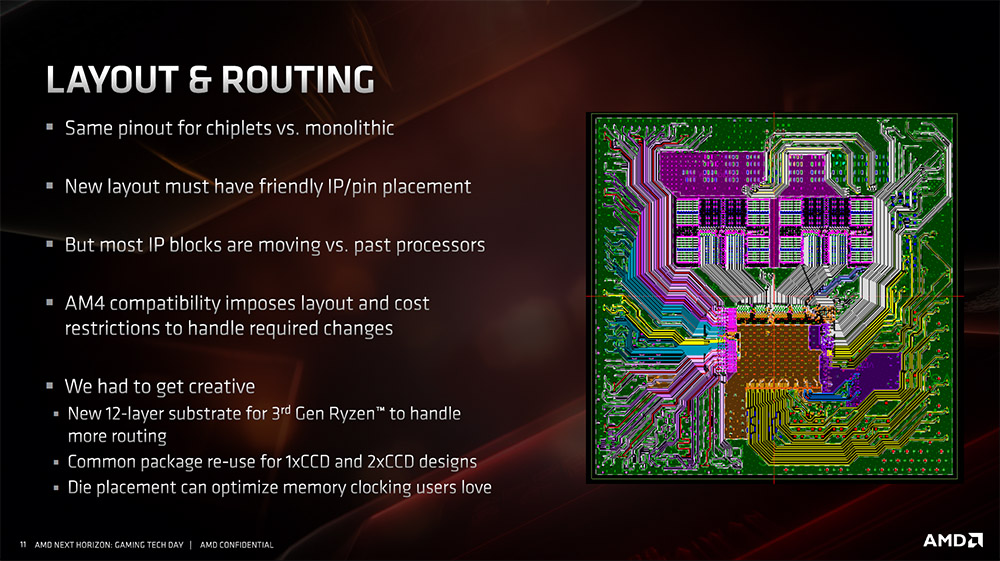

Zen 2 實質上是各單元的精進與強化,但改以 Chiplet 設計的 7nm CCD 與 12nm cIOD,更考驗著 AMD 如何實現在 AM4 腳位上。因此,這一代 Ryzen 處理器,為了維持相同的針腳,採用著 12 層電路板(substrate),據悉全球只有兩家 Vendor 可製作 microPGA 符合 Ryzen 所需。

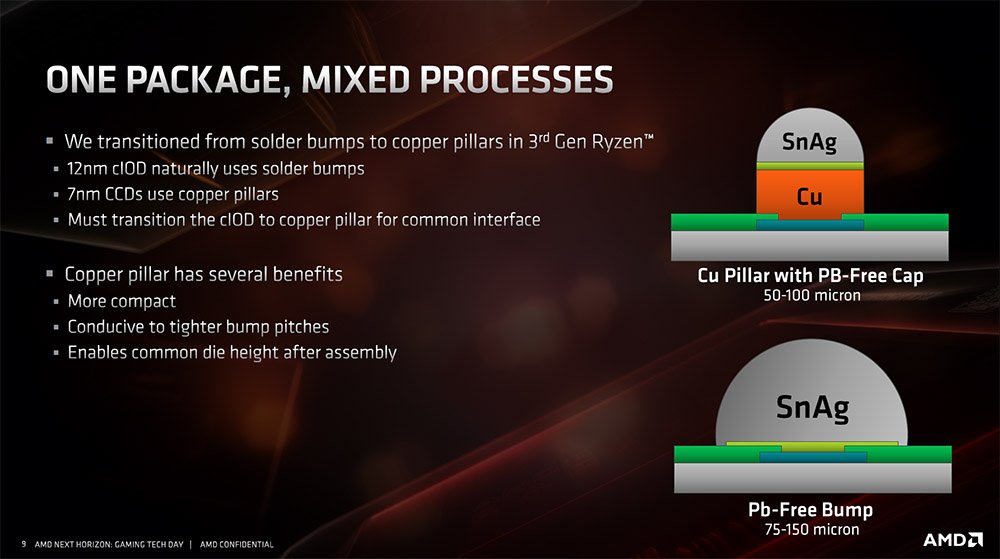

而其中 12nm 採用 150um 的 Solder Bump、7nm 使用 130um 的 Copper Pillar 針腳,確保線路、針腳可相容於現有的 AM4 腳位。

↑ 採用更緊密的針腳,讓 Zen 2 依舊相容 AM4。

↑ 混合著 Solder Bump 與 Copper Pillar 的封裝。

↑ 電路板路線圖。

小結

小結

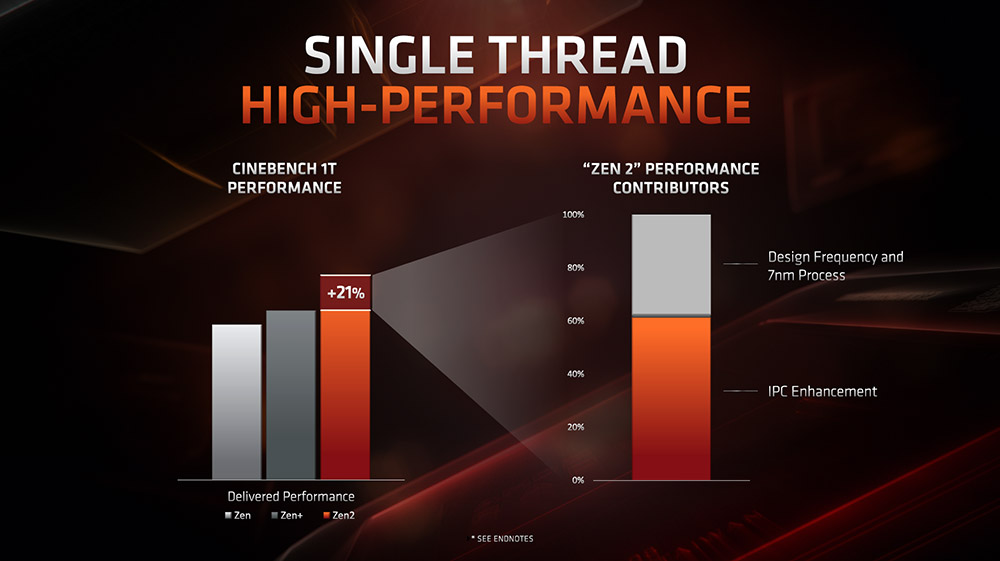

第三代 Ryzen 處理器效能的提升,其中 60% 可歸功於 Zen 2 架構的改良,而 40% 則是頻率與 7nm 製程的提升。

Zen2 比起 Zen 有著 15% IPC 提升,而實際效能比起 Zen+ 則有著 21% 的成長;至於實際效能比較就留待 7/7 號效能解禁時在跟各位報告了。

↑ 單核心效能提升。